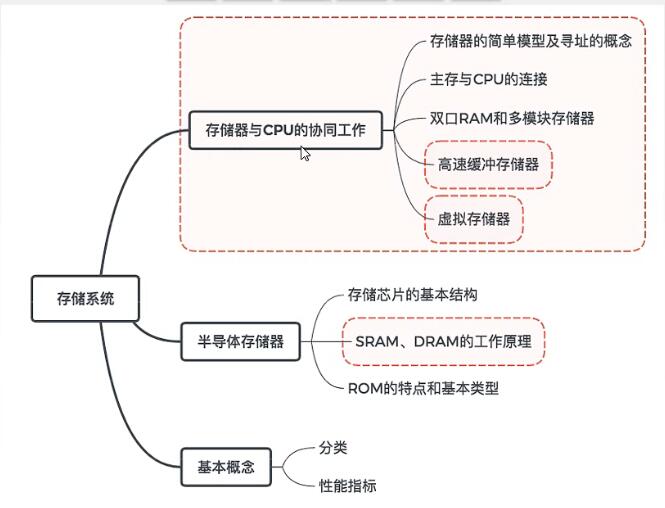

计算机组成原理存储系统

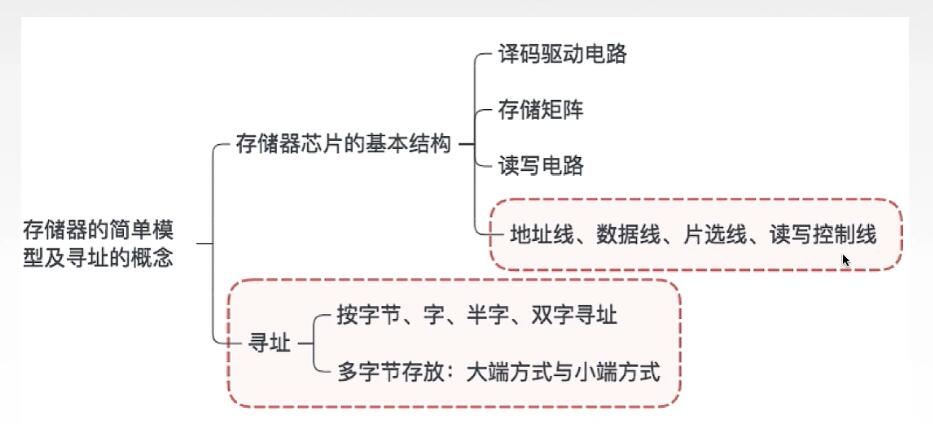

主存模型和寻址

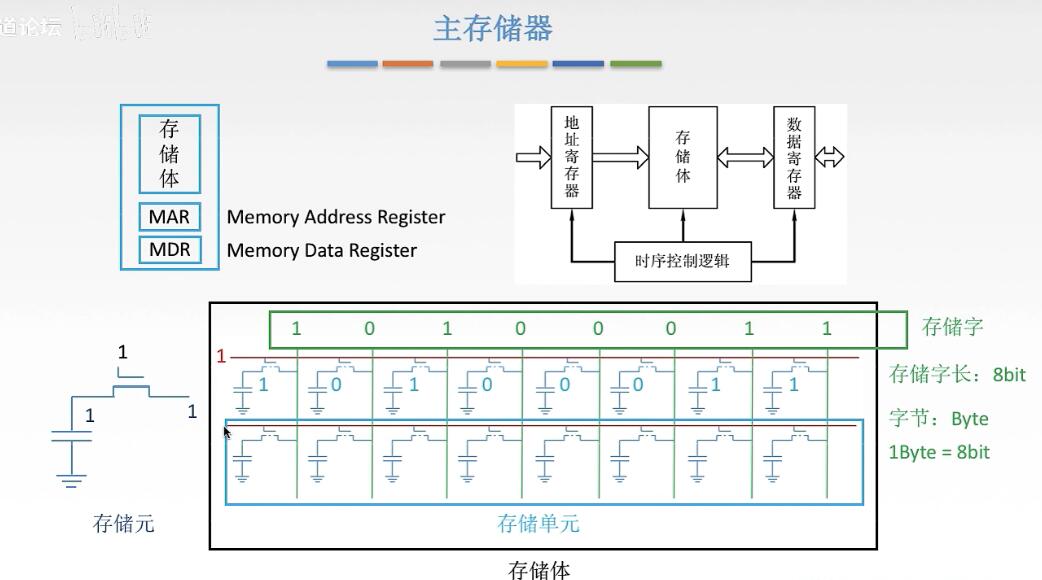

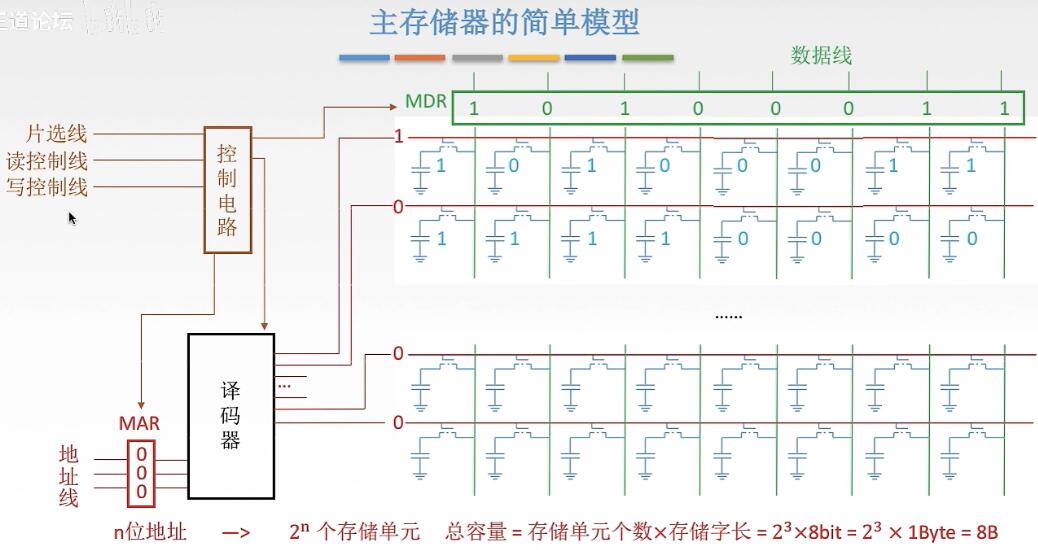

- 一个能够完成二进制位读写的单元为存储元,存储体由多个存储元构成。

其中时序控制逻辑如图:

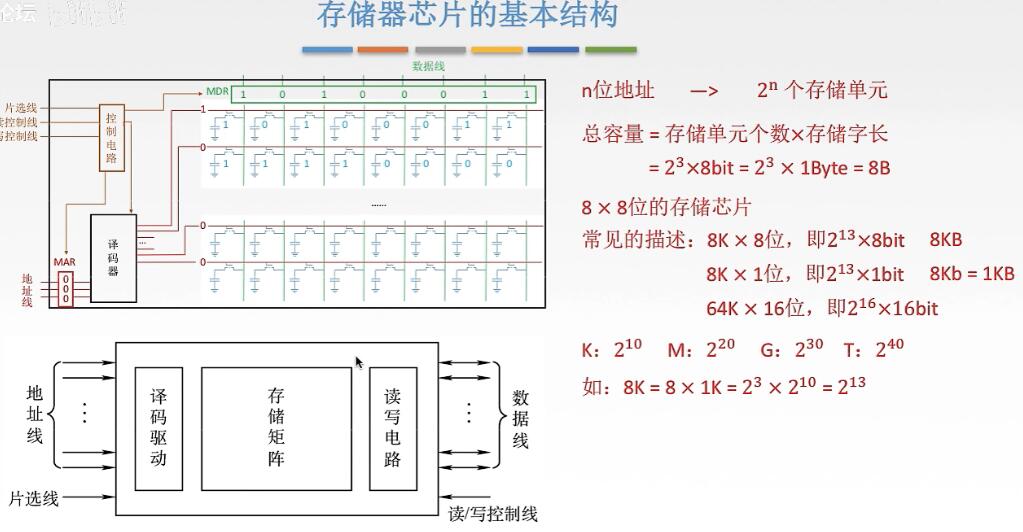

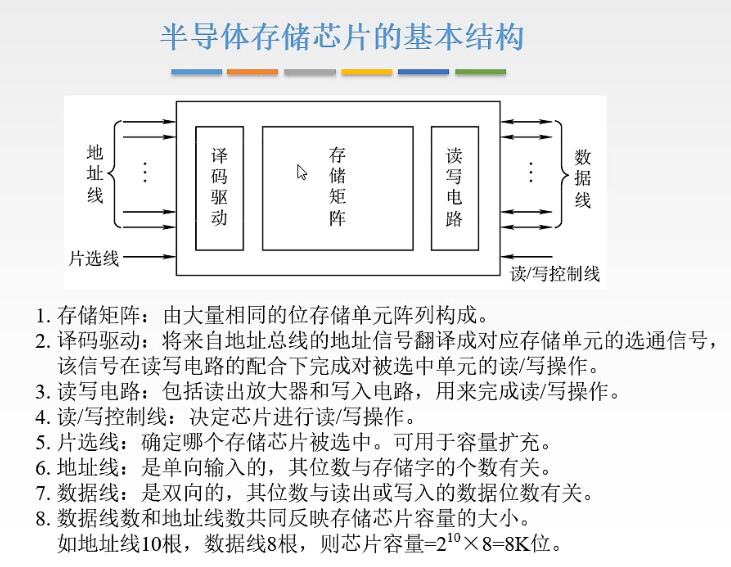

其中时序控制逻辑如图:  封装称为存储器芯片。其中有若干接口线:地址线,数据线,片选线,读写控制线。总容量=存储单元个数X存储字长。

封装称为存储器芯片。其中有若干接口线:地址线,数据线,片选线,读写控制线。总容量=存储单元个数X存储字长。

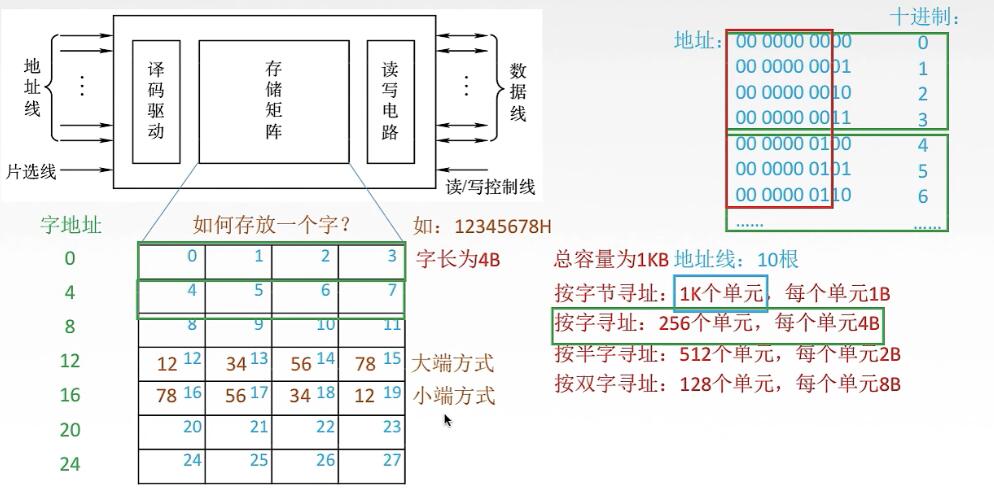

- 寻址:如何定位到一个存储单元(一行)

按照字节寻址,每单元1B。按照字寻址,每个单元4B。还有半字2B和双字8B。根据单元个数求出地址线根数,分出若干组,求出每组的组号作为字地址。

而此时如何存放一个字?字长为4B,可以根据大端和小端方式来存放字。

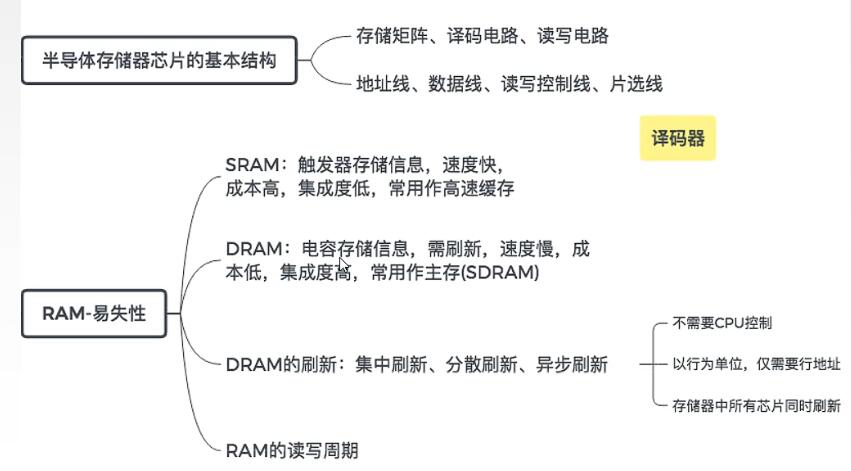

半导体存储器RAM

- 半导体存储器芯片的基本结构:

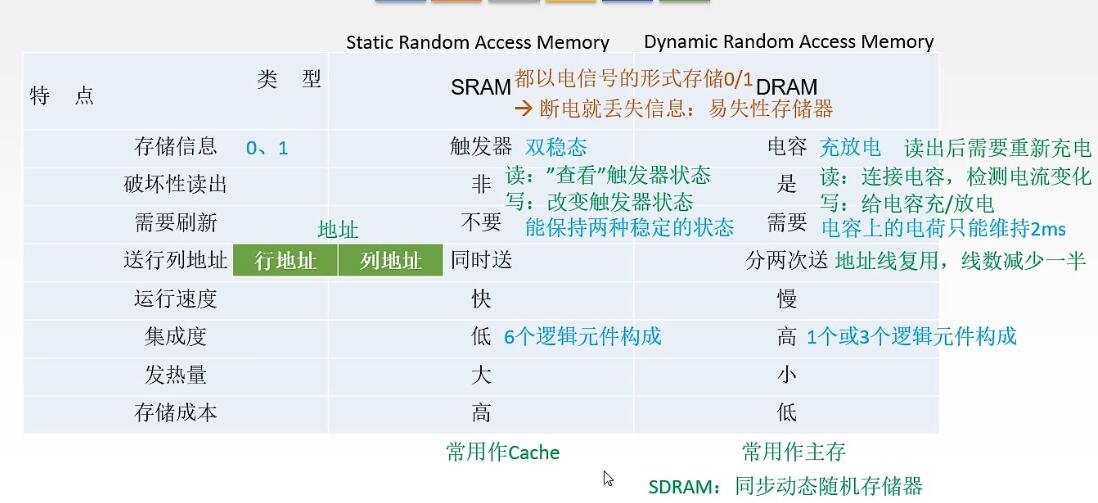

- SRAM和DRAM比较:

- DRAM的刷新:

①刷新周期2ms。

②每次刷新一行存储单元,并且根据行列等长地址定位(减少选通线的数量)。

③根据硬件,读出一行之后重新写入,占用一个读/写周期。

④整个刷新周期每行刷新一次即可。半导体存储器ROM

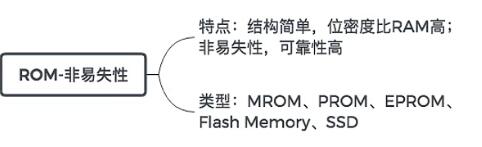

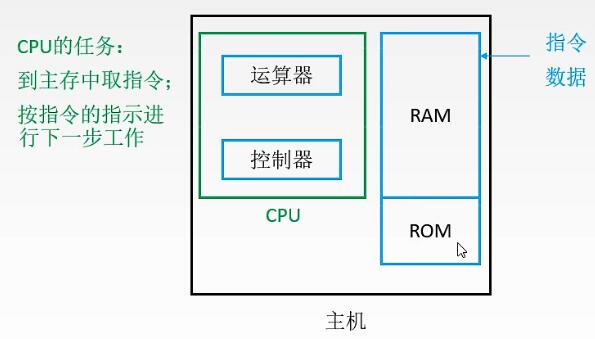

RAM是易失性存储器,断电丢失数据,所以不能作为主存,所以出现了ROM(存储开机之后需要初始的固定信息)。

RAM是易失性存储器,断电丢失数据,所以不能作为主存,所以出现了ROM(存储开机之后需要初始的固定信息)。

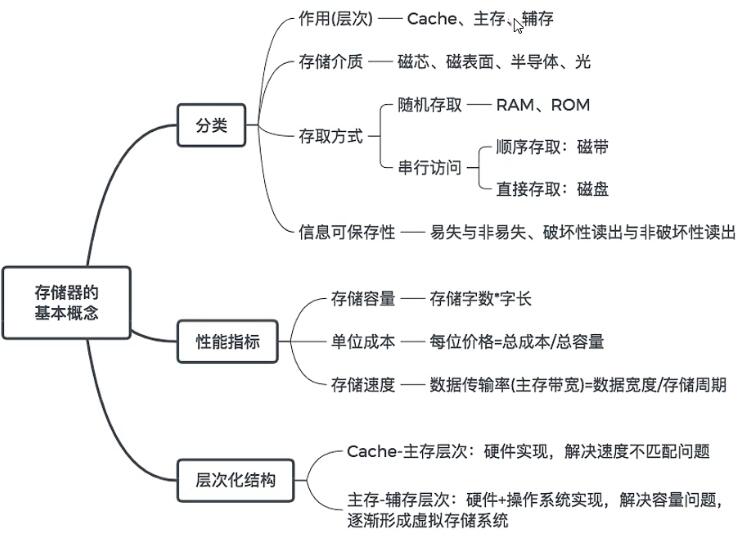

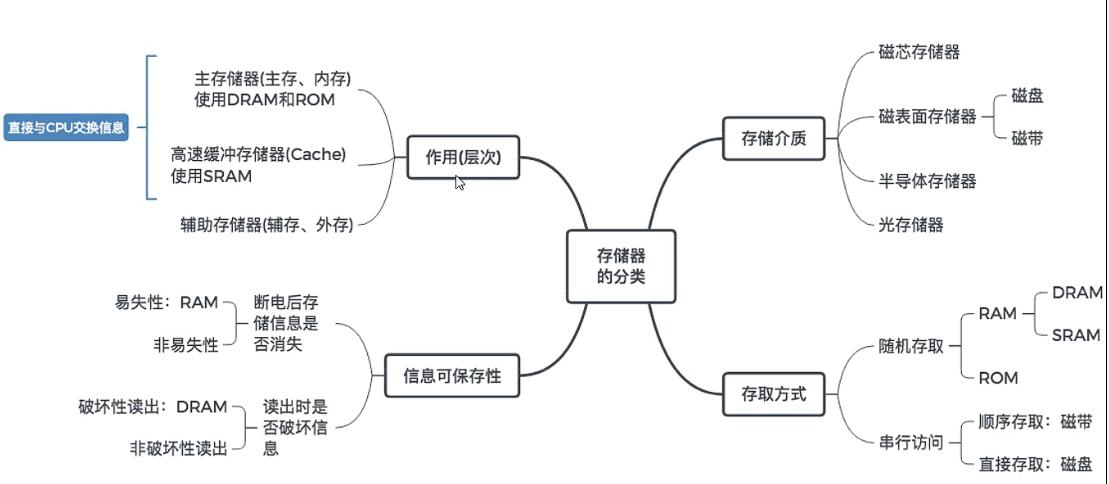

存储系统基本概念

- 分类:

使用不同材料:①磁表面存储器:磁盘(直接存取)磁带(顺序存储)。②磁芯存储器。③半导体存储器(随机存储ROM,RAM)。④光存储器。

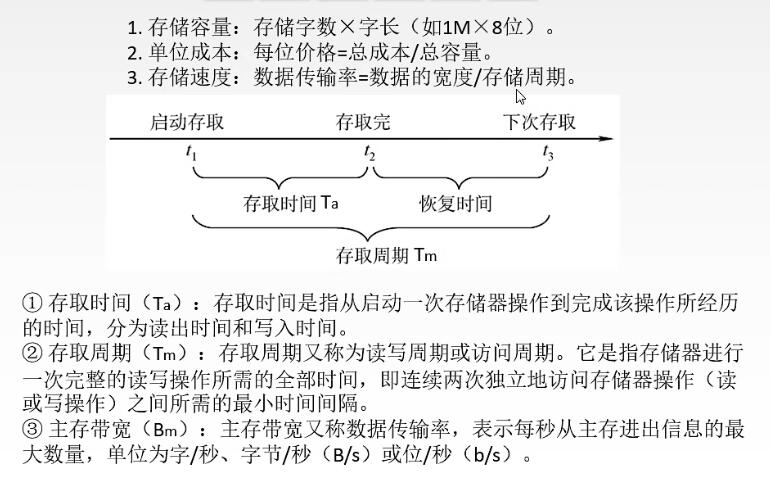

- 性能指标:

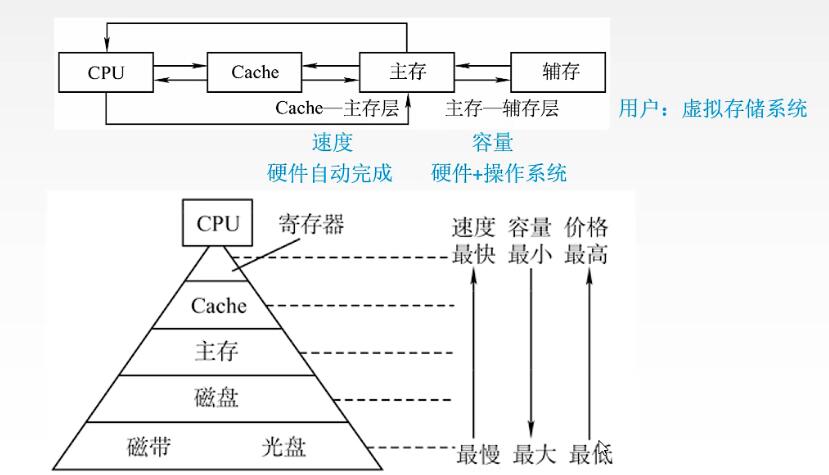

- 存储器层次化结构:

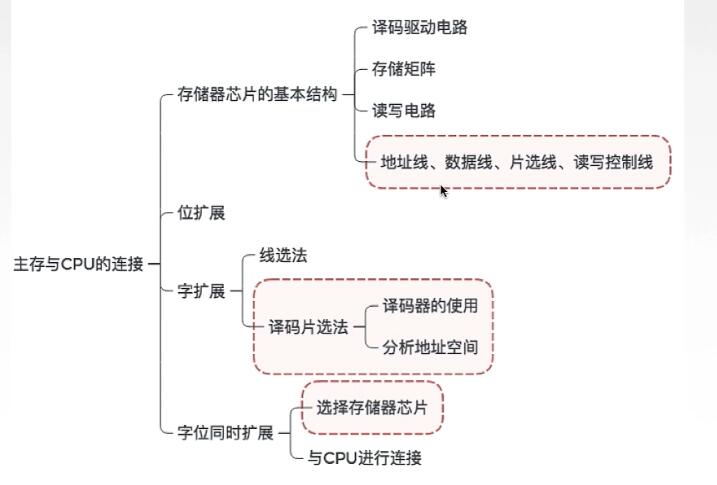

主存和CPU的连接

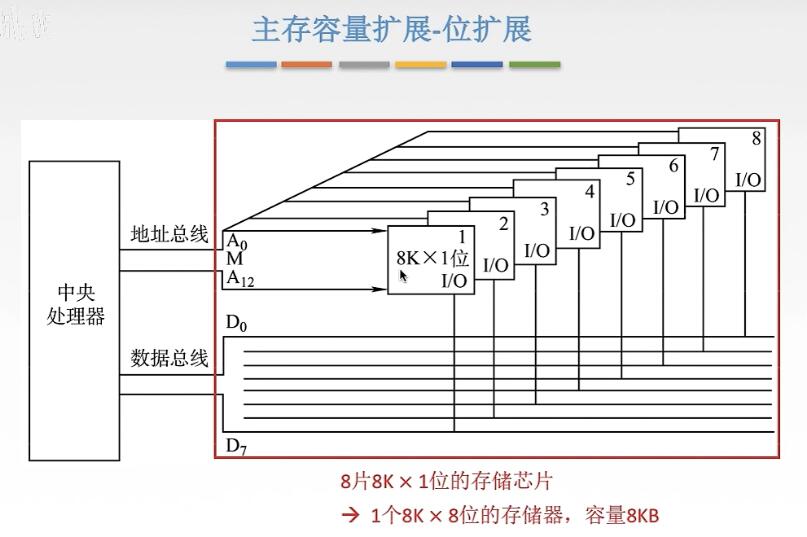

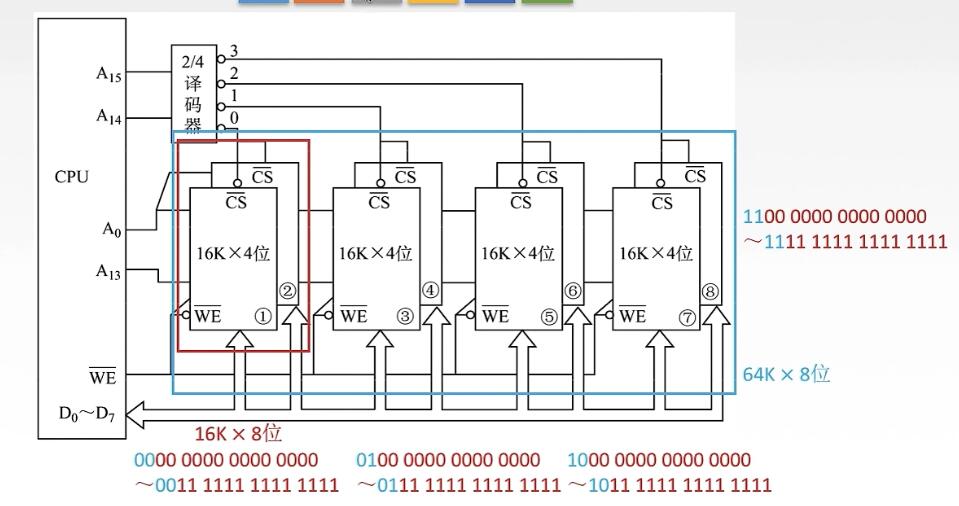

- CPU和存储器之间地址线和数据线分别连接,可以通过位扩展和字扩展。

位扩展: 字扩展:

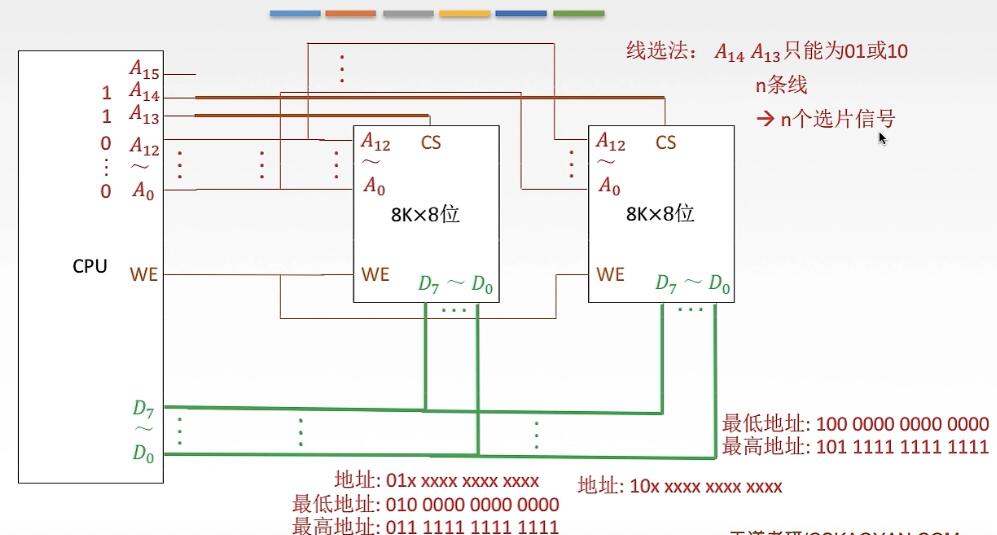

字扩展:

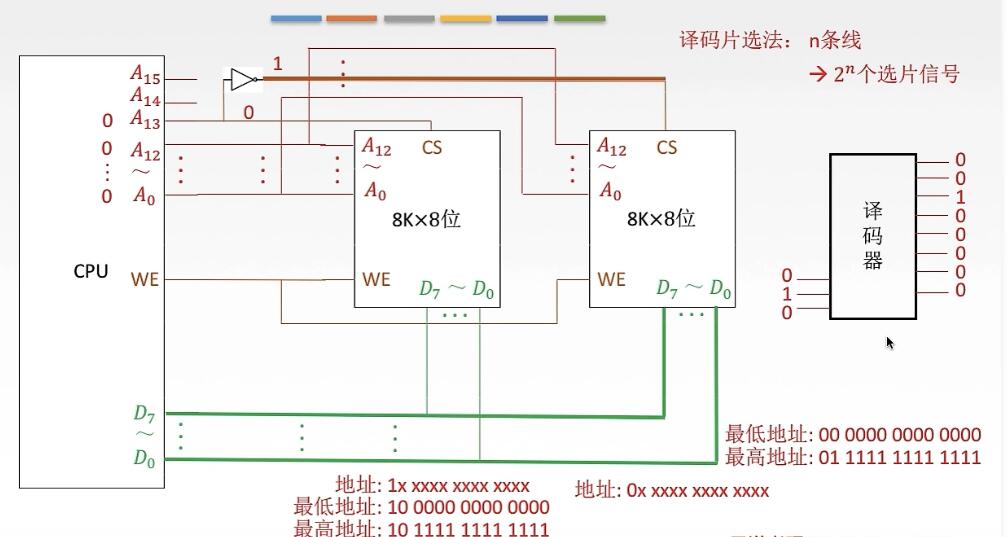

①线选法:n条线控制n个选片信号 ②译码器片选法:n条线控制2的n次方个选片信号

②译码器片选法:n条线控制2的n次方个选片信号  字位同时扩展:

字位同时扩展:

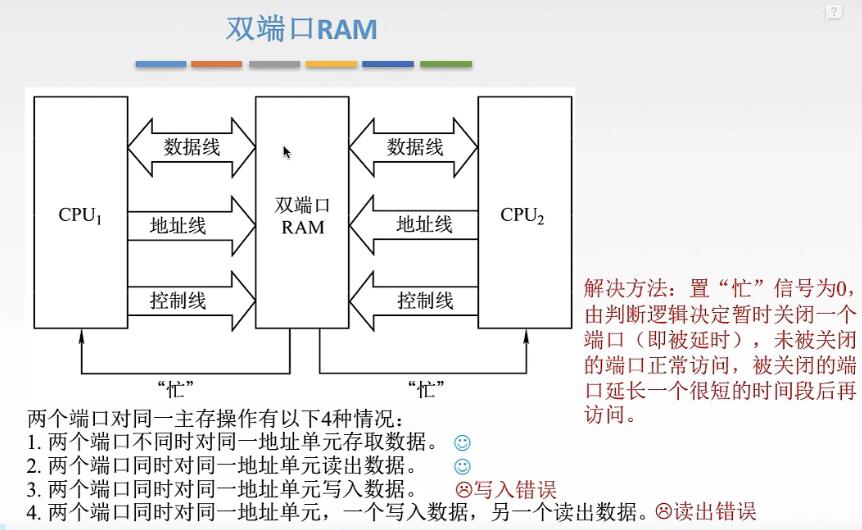

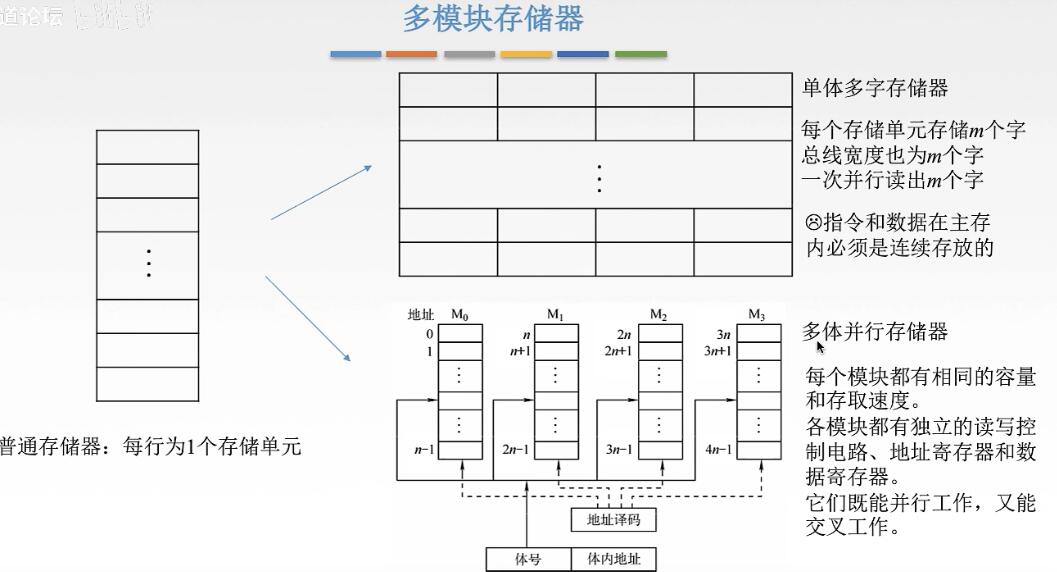

双端口RAM和多模块存储器

两者都是为了提高存储器的工作速度。

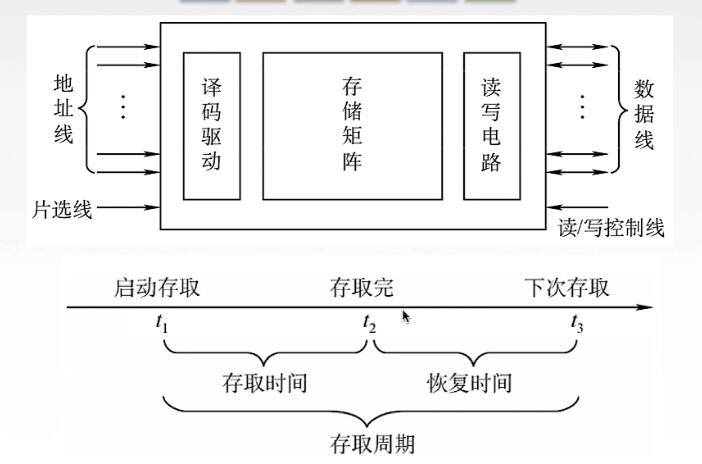

存取周期:存取时间+恢复时间(利用恢复时间存取其他数据)

- 双端口RAM:

- 多模块存储器:

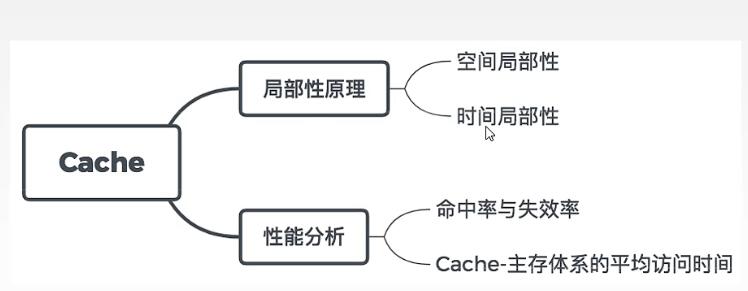

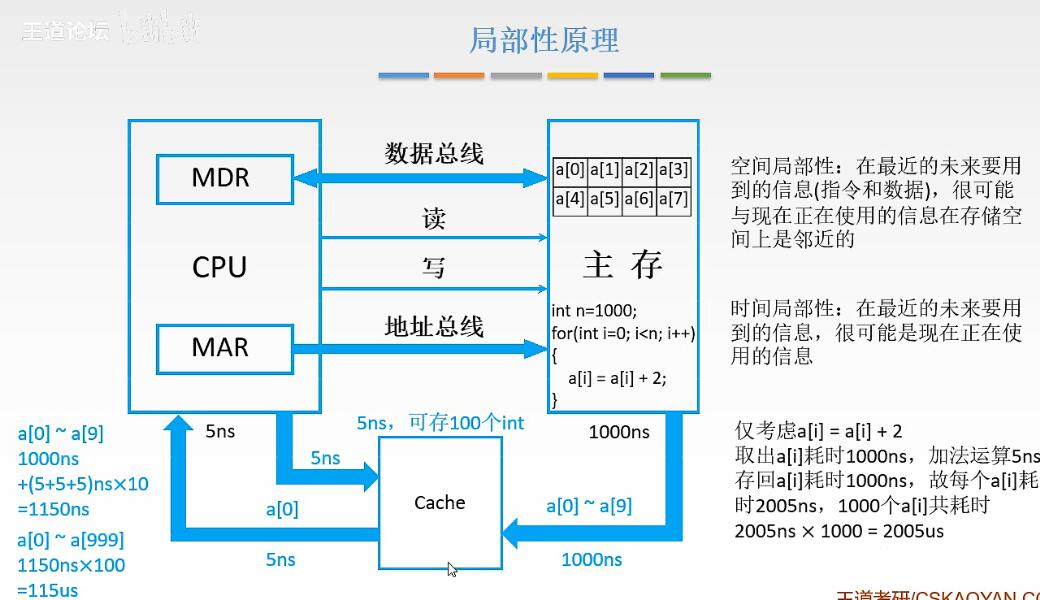

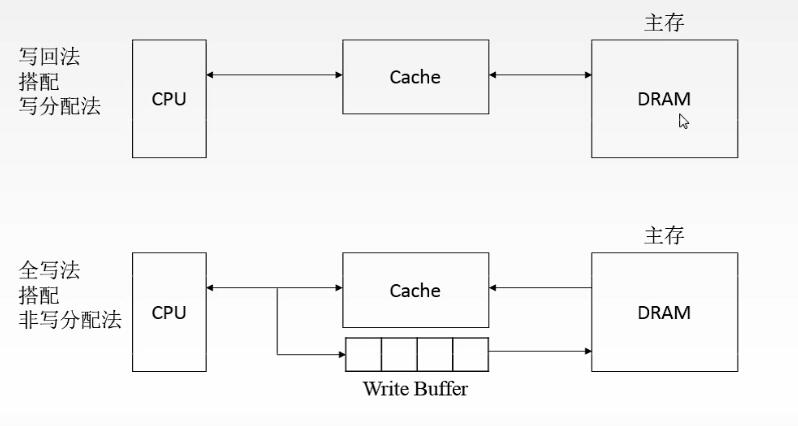

高速缓冲存储器局部性原理

把主存数据调入Cache之后,使CPU和Cache交互处理数据。

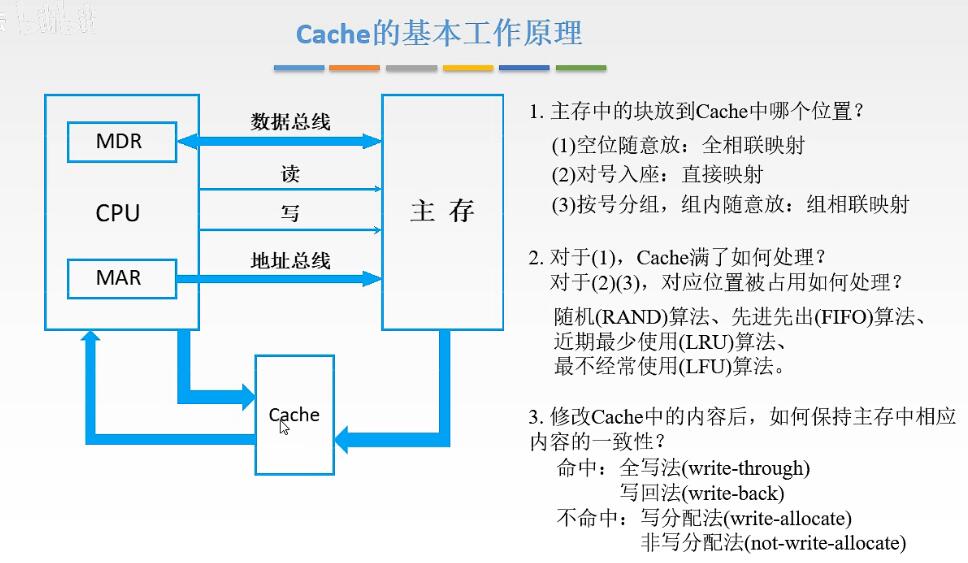

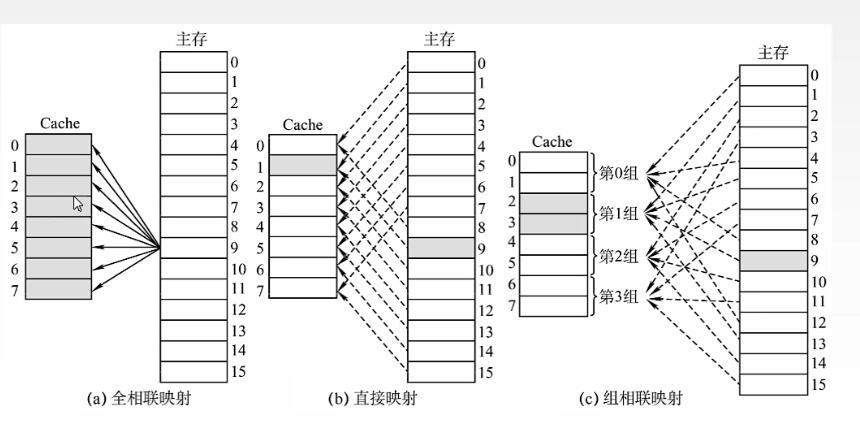

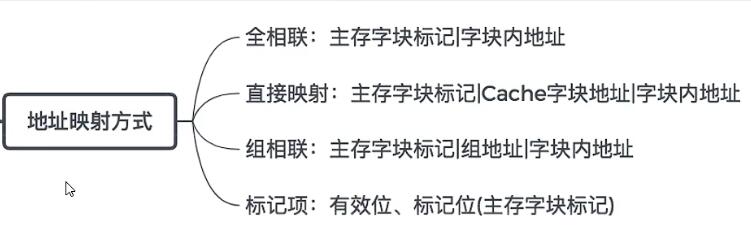

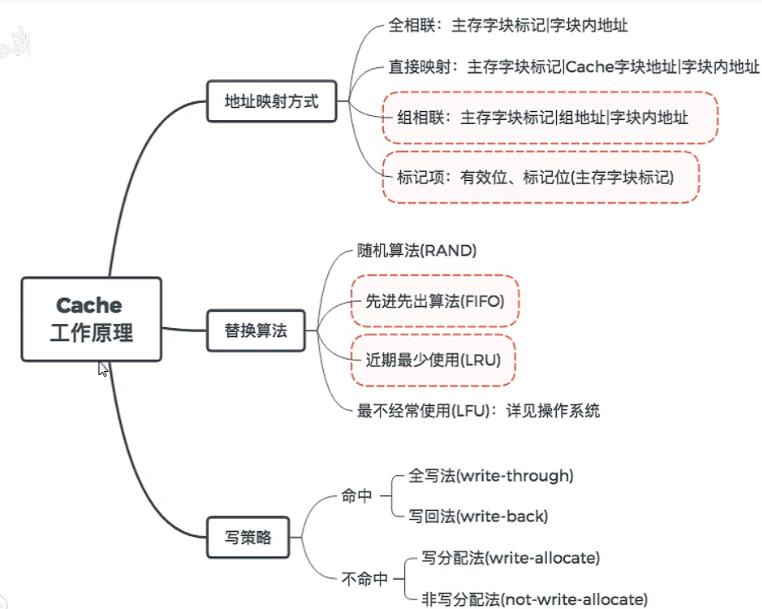

Cache和主存之间的地址映射

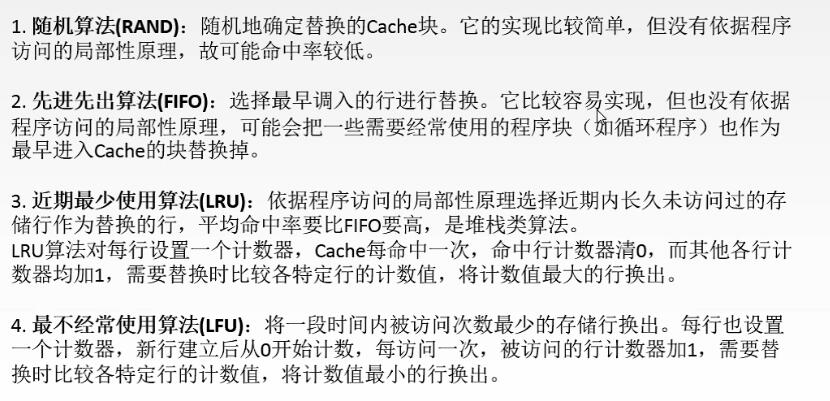

Cache替换算法

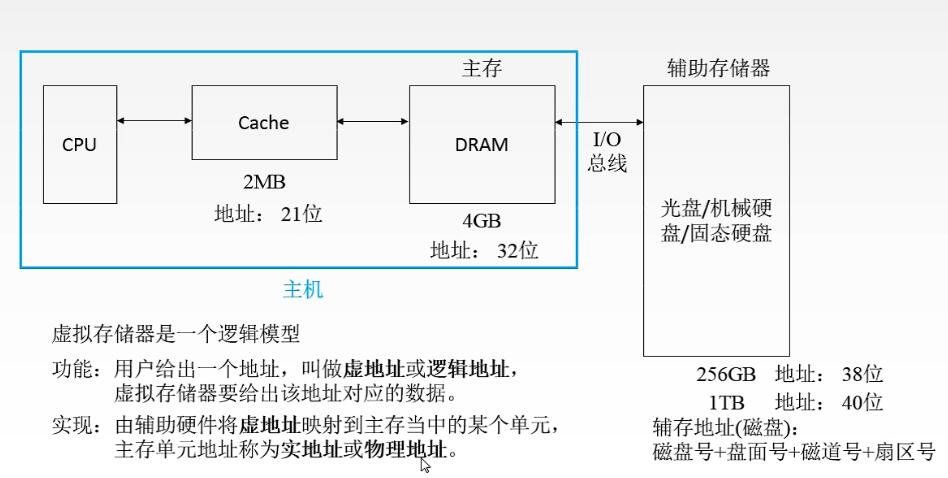

虚拟存储器

根据划分单位不同,分为三种不同虚拟存储器:

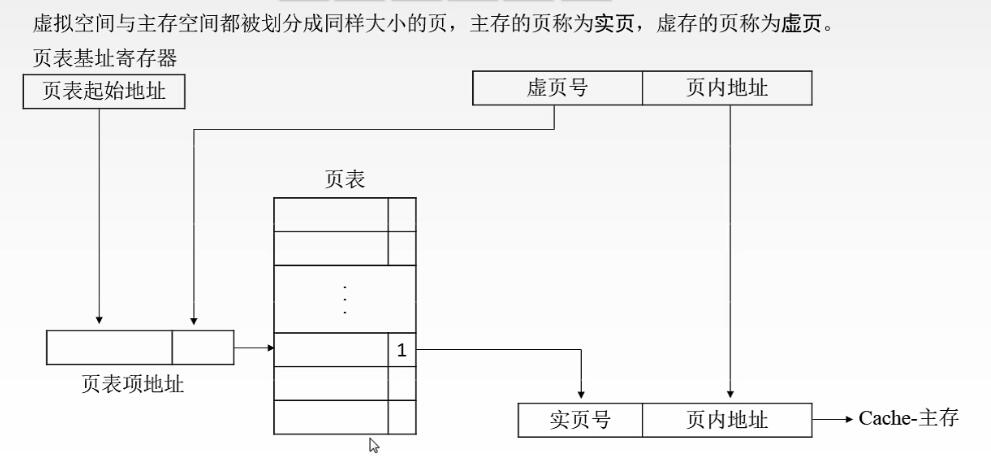

- 页式虚拟存储器:

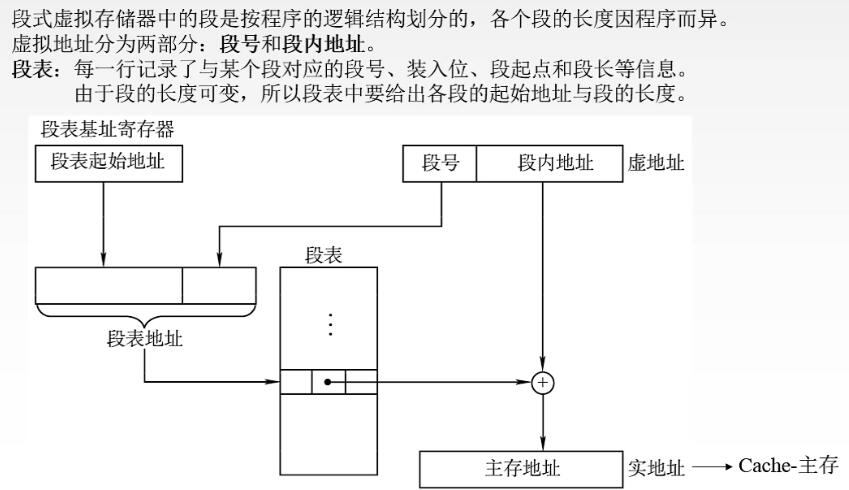

- 段式虚拟存储器:

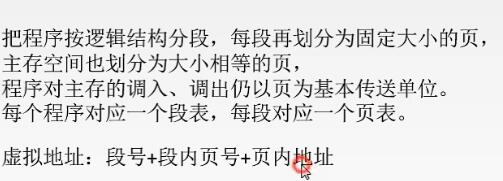

- 段页式虚拟存储器:

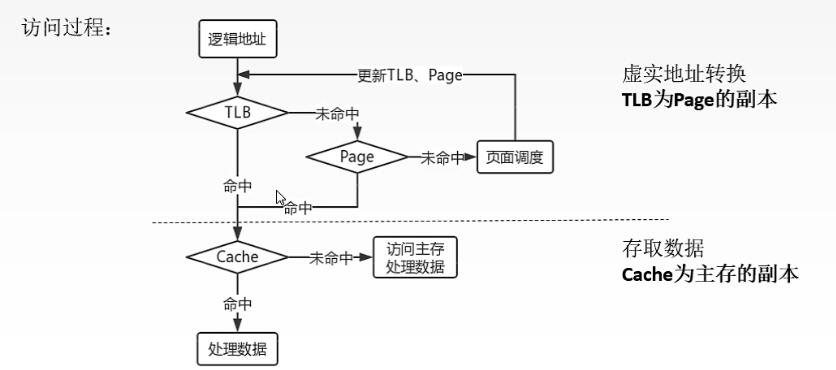

快表TLB:

快表TLB:

页表,段表放在主存中,收到虚拟地址之后要先访问主存,查询页表和段表进行转换,放在内存中的表称为慢表。为了提高变换速度,用高速缓冲存储器存放常用的页表项,形成了快表TLB。